Pages: [1] 2 3 4

|

|

|

|

Author

Author

|

Topic: Odyssey II - Inbetriebnahme (Read 12871 times)

|

|

hb9trt

Urgestein

Offline Offline

Posts: 649

Ich liebe dieses Forum!

|

|

Odyssey II - Inbetriebnahme

« on: 13. May 2020, 20:32:20 »

|

|

Keine Angst, soweit bin ich noch nicht. Aber ich denke, dieses Thema brauchen wir dann auch noch.

Vorgängig kann hier mal alles reingeschrieben werden, was man sich besorgen muss um den Odyssey II in Betrieb zu nehmen, also nach der Lötarbeit.

- Programmer für den FPGA

- Programmer für den PIC

- Software für die Programmer

Weiter wie kompiliert man die Sourcen für den FPGA? Den PIC? Oder gibts ev. auch bereits eine art binaries welche dann auf einfache Art und weise auf die Cips geladen werden können. Etc.

Gruss

Reto

|

|

Logged Logged

|

|

|

|

|

|

SP9BSL

positron

alter Hase

Offline Offline

Posts: 443

|

|

Re:Odyssey II - Inbetriebnahme

« Reply #2 on: 14. May 2020, 18:05:36 »

|

|

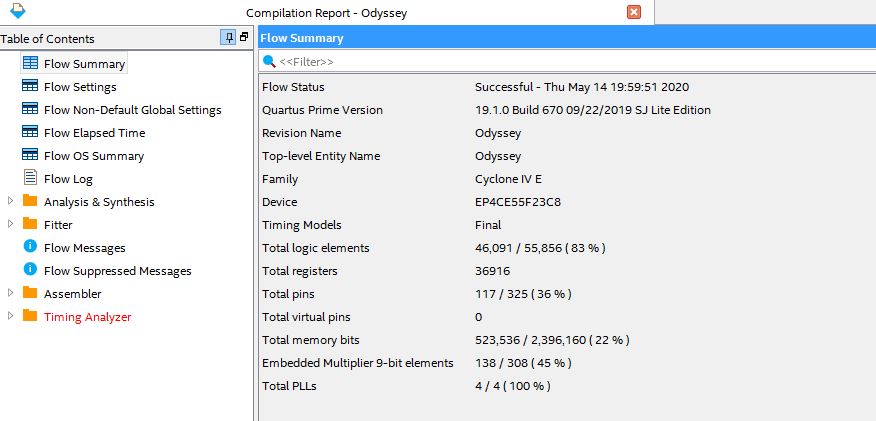

For the FPGA, I see complete sources on David's github. There are few versions suporting different protocols I think. Also I see the .pof files inside the archives (.pof=programming file for external flash device).

For programming simply download and install the Quartus prime LITE with device support file for Cyclone IV. The latest lite version available for free is 19.1.

Then run the programmer and open .pof file. Select device for the project (you must check this, but probably one of theEPCS devices) The programmer hardware was mentioned somewhere that cheap clone should work (search for Altera usb blaster for few bucks).

In case of development, you must be patient  The build time is very long, took 18min using i7MQ CPU... The FPGA usage is 83%. The build time is very long, took 18min using i7MQ CPU... The FPGA usage is 83%.

|

73 Slawek

|

|

|

SP9BSL

positron

alter Hase

Offline Offline

Posts: 443

|

|

Re:Odyssey II - Inbetriebnahme

« Reply #3 on: 14. May 2020, 18:09:37 »

|

|

I see the programmer is set up properly for EPCS64. Just connect the programmer and voila...

|

|

Logged Logged

|

73 Slawek

|

|

|

hb9trt

Urgestein

Offline Offline

Posts: 649

Ich liebe dieses Forum!

|

|

Re:Odyssey II - Inbetriebnahme

« Reply #4 on: 14. May 2020, 21:01:22 »

|

|

Also bei mir dauerte das nur etwa 3 Minuten

Ich habe einen i7 2te Generation... Also 2013 oder 14....uralt Teil.. Trotzdem der PC mit dem ich das tägliche Geschäft erledige. War damals zugegeben eine Rennmaschine.

Müsste mal mit dem Surface Pro 7 probieren. I7 10te generation. Bin nicht mal sicher, dass es damit schneller geht  .... ....

Gruss Reto

|

|

Logged Logged

|

|

|

|

SP9BSL

positron

alter Hase

Offline Offline

Posts: 443

|

|

Re:Odyssey II - Inbetriebnahme

« Reply #5 on: 15. May 2020, 09:02:11 »

|

|

Reto,

did you use the commercial version? I tested yesterday with AMD FX6 CPU and the result is similar: build time about 18 mins for full build, not analysis. When run analysis only (for simulation) it takes about 3 mins. The most time consuming process is Fitter routing.

I use freely available lite version. It uses only single CPU core for build. The commercial version (for few thousands $) uses all available resources, thus it runs much faster during build.

|

| « Last Edit: 15. May 2020, 09:03:29 by SP9BSL » |

Logged Logged

|

73 Slawek

|

|

|

|

|

hb9trt

Urgestein

Offline Offline

Posts: 649

Ich liebe dieses Forum!

|

|

Re:Odyssey II - Inbetriebnahme

« Reply #7 on: 20. May 2020, 11:22:28 »

|

|

@Slawek

Maybe I only did the analysis. I can't remember, but I can try again

@Thomas

Du brauchst dann nochmals 500MB für die Cyclone IV device Unterstützung.

@Andreas

Schön, dass Dich das Projekt auch interessiert. Ich weiss, ohne Open Source wäre es bei Dir "no go". Und zugegebenermassen ist das keine Schlechte Haltung in der Hobby Welt. Kommerziell sieht es da halt anders aus. Da will man die Entwicklung vor allem nicht mit den Mitbewerbern teilen

Trotzdem werde ich vermutlich nicht in der Lage sein, hier etwas zu ändern, ohne dass dann am Schluss gar nichts mehr funktioniert.

Interessant wäre, wenn man die UHSDR Software für einen Standalone Direktsampler TRX einsetzen könnte. Dazu fehlt mir aber das wissen, inwieweit die Software bereits Decodierung übernimmt und wo da genau die Schnittstelle wäre. Ich gehe davon aus, dass die GUI hier nur noch Steuerung und Anzeige ist, aber alles was codiert und decodiert wird im FPGA abgeht. So genau habe ich da nicht recherchiert. Zumindest bei dem Direktsampler von HB9CBU aus dem Jahr 2009 ist das so, die GUI ist marginal und der Prozessor dafür ist nur gerade für die Bedienung, die Menüs und die Anzeige. Muss aber nicht allgemein gültig sein.

(Der TRX von HB9CBU ist übrigens auch heute noch ein "Referenz" TRX, zumindest für mich und für die meisten die den haben auch. Geht locker als Messempfänger und Messsender durch mit seiner Genauigkeit. Vor allem für den Hobby Gebrauch kann man den so einsetzen.

Und dass Herr Rohde davon begeistert ist und einen besitzt zeigt mir, dass er nicht schlecht sein kann.  Seit da bin ich von der Direktsampler Technik begeistert.) Seit da bin ich von der Direktsampler Technik begeistert.)

Gruss

Reto

|

|

Logged Logged

|

|

|

|

SP9BSL

positron

alter Hase

Offline Offline

Posts: 443

|

|

Re:Odyssey II - Inbetriebnahme

« Reply #8 on: 20. May 2020, 12:40:38 »

|

|

Interessant wäre, wenn man die UHSDR Software für einen Standalone Direktsampler TRX einsetzen könnte.

|

|

Reto,

this already happened, I will show the things in the June. With friends here in Poland and in the Germany we are assembling the first sets (alpha phase). I hate to show untested things. I will open separate thread here and on my www page.

|

|

Logged Logged

|

73 Slawek

|

|

|

hb9trt

Urgestein

Offline Offline

Posts: 649

Ich liebe dieses Forum!

|

|

Re:Odyssey II - Inbetriebnahme

« Reply #9 on: 20. May 2020, 13:06:13 »

|

|

Hello Slawek,

You build Odyssey II ore another project?

I get the Boards next Monday and next Week also most of the Parts. I don't know If I start next week...;)

I also compiled the project again and now it takes 17:14 Minutes. But I have many warnings like this:

Warning (10036): Verilog HDL or VHDL warning at Odyssey.v(148): object "RAND" assigned a value but never read

Warning (10858): Verilog HDL warning at Odyssey.v(925): object frequency_change used but never assigned

Warning (10230): Verilog HDL assignment warning at Odyssey.v(786): truncated value with size 17 to match size of target (16)

Warning (10230): Verilog HDL assignment warning at Odyssey.v(787): truncated value with size 17 to match size of target (16)

Warning (10030): Net "frequency_change" at Odyssey.v(925) has no driver or initial value, using a default initial value '0'

Warning (10230): Verilog HDL assignment warning at iambic.v(138): truncated value with size 32 to match size of target (16)

Warning (10230): Verilog HDL assignment warning at iambic.v(139): truncated value with size 32 to match size of target (18)

Warning (10230): Verilog HDL assignment warning at iambic.v(192): truncated value with size 32 to match size of target (18)

Warning (10230): Verilog HDL assignment warning at Led_control.v(48): truncated value with size 32 to match size of target (25)

Warning (10230): Verilog HDL assignment warning at Led_control.v(49): truncated value with size 32 to match size of target (25)

Warning (12011): Net is missing source, defaulting to GND

Warning (12110): Net "Rx_Audio_Used[12]" is missing source, defaulting to GND

Warning (12110): Net "Rx_Audio_Used[11]" is missing source, defaulting to GND

Warning (12011): Net is missing source, defaulting to GND

Warning (12110): Net "Rx_Audio_Used[12]" is missing source, defaulting to GND

Warning (12110): Net "Rx_Audio_Used[11]" is missing source, defaulting to GND

Warning (12011): Net is missing source, defaulting to GND

Warning (12110): Net "Rx_Audio_Used[12]" is missing source, defaulting to GND

Warning (12110): Net "Rx_Audio_Used[11]" is missing source, defaulting to GND

Warning (12011): Net is missing source, defaulting to GND

Warning (12110): Net "Rx_Audio_Used[12]" is missing source, defaulting to GND

Warning (12110): Net "Rx_Audio_Used[11]" is missing source, defaulting to GND

Warning (332174): Ignored filter at Odyssey.sdc(41): tx_pll_c1 could not be matched with a pin

Warning (332049): Ignored create_generated_clock at Odyssey.sdc(41): Argument -source is an empty collection

Info (332050): create_generated_clock -name PHY_TX_CLOCK -source [get_pins {tx_pll_c1}] [get_ports {PHY_TX_CLOCK}]

Warning (332174): Ignored filter at Odyssey.sdc(49): tx_pll_inclk could not be matched with a pin

Warning (332174): Ignored filter at Odyssey.sdc(49): tx_pll_c0 could not be matched with a pin

Critical Warning (332049): Ignored create_generated_clock at Odyssey.sdc(49): Argument <targets> is an empty collection

Info (332050): create_generated_clock -name clock_125_MHz_0_deg -phase -67.5 -source [get_pins {tx_pll_inclk}] [get_pins {tx_pll_c0}]

Warning (332049): Ignored create_generated_clock at Odyssey.sdc(49): Argument -source is an empty collection

Critical Warning (332049): Ignored create_generated_clock at Odyssey.sdc(51): Argument <targets> is an empty collection

Info (332050): create_generated_clock -name clock_125_MHz_90_deg -phase 90 -source [get_pins {tx_pll_inclk}] [get_pins {tx_pll_c1}]

Warning (332049): Ignored create_generated_clock at Odyssey.sdc(51): Argument -source is an empty collection

Warning (332174): Ignored filter at Odyssey.sdc(54): PHY_TX_CLOCK could not be matched with a clock

Warning (332049): Ignored set_output_delay at Odyssey.sdc(54): Argument -clock is not an object ID

Info (332050): set_output_delay -clock PHY_TX_CLOCK -max 1.0 [get_ports {PHY_TX}]

Warning (332174): Ignored filter at Odyssey.sdc(49): tx_pll_c0 could not be matched with a pin

Critical Warning (332049): Ignored create_generated_clock at Odyssey.sdc(49): Argument <targets> is an empty collection

Info (332050): create_generated_clock -name clock_125_MHz_0_deg -phase -67.5 -source [get_pins {tx_pll_inclk}] [get_pins {tx_pll_c0}]

Warning (332049): Ignored create_generated_clock at Odyssey.sdc(49): Argument -source is an empty collection

Critical Warning (332049): Ignored create_generated_clock at Odyssey.sdc(51): Argument <targets> is an empty collection

Info (332050): create_generated_clock -name clock_125_MHz_90_deg -phase 90 -source [get_pins {tx_pll_inclk}] [get_pins {tx_pll_c1}]

Warning (332049): Ignored create_generated_clock at Odyssey.sdc(51): Argument -source is an empty collection

Warning (332174): Ignored filter at Odyssey.sdc(54): PHY_TX_CLOCK could not be matched with a clock

Critical Warning (332148): Timing requirements not met

Info (11105): For recommendations on closing timing, run Report Timing Closure Recommendations in the Timing Analyzer.

Only a few examples. There are much more such Warnings. I compiled it with 19.1 and the original was created in 18.1. Maybe there are some settings I have to do, at this start I only load the project and compiled it.

vy 72

Reto

|

|

Logged Logged

|

|

|

|

|

|

SP9BSL

positron

alter Hase

Offline Offline

Posts: 443

|

|

Re:Odyssey II - Inbetriebnahme

« Reply #11 on: 20. May 2020, 20:28:57 »

|

|

Hi Reto,

the high count of warnings are caused by defined but not used nodes (ports) in verilog modules - width mismatch, not nice but no need to take care of it. The critical warnings I see the pll definition which has defined output port but not used, this may have impact on overall timing of PLL. I think some modules were copied from N2ADR project but not worked out to match to the Odyssey project - not nice too.

I see you have about 17 mins build time and now I see it ok, no need to upgrade my CPU

Regarding runing UHSDR with conjunction to direct digital conversion, my project is not based on Odyssey but uses the same IP core by N2ADR/VE3NEA based on scientific work of Darrel Harmon/Cathy Moss. This is simply not good idea to write this by yourself, it is like reinventing the wheel... David and many others used it, why shouldn't I use it too? I use my own board with cheap EP4CE15 chip (LQFP144EP) and ADC6145 ADC. As said earlier I will show working devicewith case and power amp. Just mentioned this because you said that UHSDR+DDC would be interesting. Sorry for hijack the thread.

|

|

Logged Logged

|

73 Slawek

|

|

|

hb9trt

Urgestein

Offline Offline

Posts: 649

Ich liebe dieses Forum!

|

|

Re:Odyssey II - Inbetriebnahme

« Reply #12 on: 20. May 2020, 21:43:37 »

|

|

@Slawek,

Ok, very interesting. We'll see if you present the project. Maybe also interesting to build.

CPU: You have to upgrade  My one is a i7 second generation My one is a i7 second generation  at least 6 or 7 years old, maybe older. But works fine for the daily work. At the moment new desktops comes with generation 9 CPU's and "better" notebooks with generation 10 CPU's. I can check if my Surface 7 does it faster, but, it's a notbook, not a formula 1 PC with the desktop CPU's which are faster than the Notebook CPU's. at least 6 or 7 years old, maybe older. But works fine for the daily work. At the moment new desktops comes with generation 9 CPU's and "better" notebooks with generation 10 CPU's. I can check if my Surface 7 does it faster, but, it's a notbook, not a formula 1 PC with the desktop CPU's which are faster than the Notebook CPU's.

@Andreas

Ja, ich vermutete auch, dass diese Warnings keinen Einfluss auf die Funktionalität haben. Es steht da ja auch in etwa: Der Pin ist nicht benutzt und wird auf masse gesetzt. Aber die eine oder andere Warnung kann man sich mal anschauen. Aber wie gesagt, ich habe mit FPGA's noch rein gar nichts gemacht. Ich habe hier noch ein Testboard mit dem MAX2, da will ich mal ein paar Gehübungen absolvieren. Habe das gleich mit dem Programmer mitbestellt, kostet nicht viel.

Gruss

Reto

|

|

Logged Logged

|

|

|

|

hb9trt

Urgestein

Offline Offline

Posts: 649

Ich liebe dieses Forum!

|

|

Re:Odyssey II - Inbetriebnahme

« Reply #13 on: 20. May 2020, 22:04:18 »

|

|

@Slawek,

My Surface Pro 7 took 10 Minutes for a full compilation. Run on battery not Powersupply. I think a modern Desktop CPU is faster.

I can't check it with linux on the surface, only as vm. But I won't install Quartus on the vm.

Interesting: I use the Lite Version, I have no licence. But:

Info (20030): Parallel compilation is enabled and will use 4 of the 4 processors detected

So the lite Version supports all Cores.

But:

Warning (292013): Feature LogicLock is only available with a valid subscription license. You can purchase a software subscription to gain full access to this feature.

Also only a warning, but a feature which is only availlable in the licensed version. Will have no impact of the project.

vy 73

Reto

|

|

Logged Logged

|

|

|

|

hb9trt

Urgestein

Offline Offline

Posts: 649

Ich liebe dieses Forum!

|

|

Re:Odyssey II - Inbetriebnahme

« Reply #14 on: 22. May 2020, 12:05:37 »

|

|

Hallo zusammen,

der PIC muss ja auch noch programmiert werden. Weiss jemand wo diese Infos sind? sind das die BL Files? Ich habe das noch nicht wirklich genau angeschaut und in den russischen Foren müsste da sicher was zu finden sein. Das ist sicher auch nocht ein Punkt den man anschauen muss. Der braucht ja auch noch einen Programmer.

Gruss

Reto

|

|

Logged Logged

|

|

|

|

Pages: [1] 2 3 4

|

|

|

|

|

|

|